xHCI debug capability 也就是 DbC,這是由 xHCI host controller 所提供的獨立但非一定必要的功能。

簡單來說,它主要是擴充來支援 USB 3.0 debug,

擴充方式是在 XHCI Controller 內必須有個 PCI Capability ID 為 0xA (Debug port) 來宣示擁有這個能力 Capability。若沒有這個 Capability ,那麼就無法支援 XHCI debug。

PCI Capability ID 可於 PCI_Code-ID_r_1_5_6_Mar_2014_ncb.pdf 的 2. Capability IDs 查表。

而 Debug Capability 長得如何呢?可以參見 eXtensible Host Controller Interface for Universal Serial Bus (xHCI) 7.6.8 來了解結構。

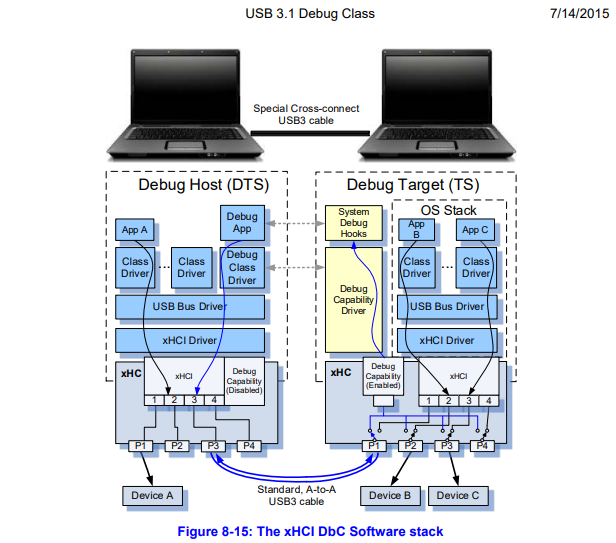

連接 USB 3 Debug Cable 並開始進行 XHCI debug (啟用 DbC) 後,在 debug host 可見到一個 debug 裝置,它是以全雙工方式進行。

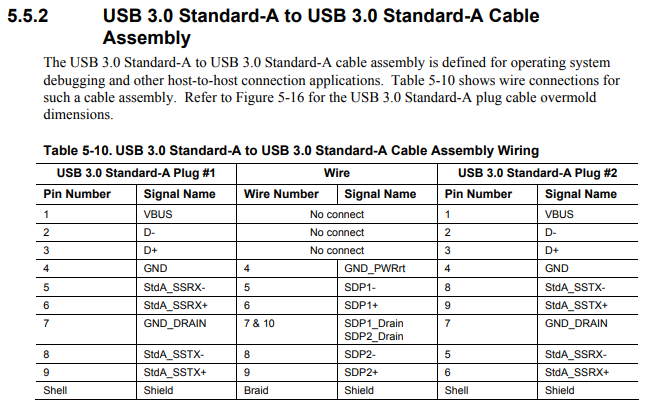

由於 USB3 已經將TX與RX分開,因此,USB 3 Debug Cable 即是略過 USB 2.0 的 VBUS/D-/D+ 不接,並把 USB3 的TX與RX交換,就像一般會說的「跳線」。

這樣的設計下來,就可以直接讓兩個 Host Port 來進行對接。而且可以使用 Debug Target 的 XHCI 上任一個 port 來進行。(不像 EHCI 時代,僅能以 Port 0 來 debug)。

[圖片來源:https://www.usb.org/sites/default/files/documents/usb_debug_class_rev_1_0_final_0.pdf]